ADM2483BRWZ

DGT ISO 2.5KV RS422/RS485 16SOIC

FEATURES

RS-485 transceiver with electrical data isolation

Complies with ANSI TIA/EIA RS-485-A and ISO 8482: 1987(E)

500 kbps data rate

Slew rate-limited driver outputs

Low power operation: 2.5 mA max

Suitable for 5 V or 3 V operations (VDD1)

High common-mode transient immunity: >25 kV/μs

True fail-safe receiver inputs

Chatter-free power-up/power-down protection

256 nodes on bus

Thermal shutdown protection

Safety and regulatory approvals

UL recognition: 2500 V rms for 1 minute per UL 1577

CSA Component Acceptance Notice 5A

IEC 60950-1 800 V rms (basic), 400 V rms (reinforced)

VDE Certificate of Conformity

DIN V VDE V 0884-10 (VDE V 0884-10): 2006-12

VIORM = 560 V peak (reinforced)

VIORM(DC) = 1500 V dc

CQC certification per GB4943.1-2011

Operating temperature range: −40°C to +85°C

APPLICATIONS

Low power RS-485/RS-422 networks

Isolated interfaces

Building control networks

Multipoint data transmission systems

GENERAL DESCRIPTION

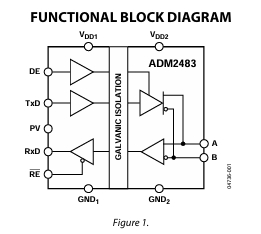

The ADM2483 differential bus transceiver is an integrated, galvanically isolated component designed for bidirectional data communication on balanced, multipoint bus transmission lines. It complies with ANSI EIA/TIA-485-A and ISO 8482: 1987(E). Using the iCoupler technology from Analog Devices, Inc., the ADM2483 combines a 3-channel isolator, a three-state differential line driver, and a differential input receiver into a single package. The logic side of the device is powered with either a 5 V or 3 V supply, and the bus side uses a 5 V supply only.

The ADM2483 is slew-limited to reduce reflections with improperly terminated transmission lines. The controlled slew rate limits the data rate to 500 kbps. The device’s input impedance is 96 kΩ, allowing up to 256 transceivers on the bus. Its driver has an active-high enable feature. The driver differential outputs and receiver differential inputs are connected internally to form a differential input/output (I/O) port.

When the driver is disabled or when VDD1 or VDD2 = 0 V, this imposes minimal loading on the bus. An active-high receiver disable feature, which causes the receive output to enter a high impedance state, is provided as well.

The receiver inputs have a true fail-safe feature that ensures a logic-high receiver output level when the inputs are open or shorted. This guarantees that the receiver outputs are in a known state before communication begins and at the point when communication ends.

- LP8557IEVM_TI(德州仪器)中文资料_英文资料_价格_PDF手册

- LAUNCHXL-F28027F TI(德州仪器)中文资料_英文资料_价格_PDF手册

- DLPDLCR160CPEVM DLP160CP TI(德州仪器)中文资料_英文资料_价格_PDF手册

- THS4631DDAEVM TI(德州仪器)中文资料_英文资料_价格_PDF手册

- DAC3482EVM TI(德州仪器)中文资料_英文资料_价格_PDF手册

- THS4302EVM TI(德州仪器)中文资料_英文资料_价格_PDF手册

- ADS7038Q1EVM-PDK_TI(德州仪器)中文资料_英文资料_价格_PDF手册

- LM3450AEV230V30/NOPB_TI(德州仪器)中文资料_英文资料_价格_PDF手册

- TPS72728DSEEVM-406_TI(德州仪器)中文资料_英文资料_价格_PDF手册

- WL1835MODCOM8A_TI(德州仪器)中文资料_英文资料_价格_PDF手册

- TAS5424BQ1DKDEVM_TI(德州仪器)中文资料_英文资料_价格_PDF手册

- ADS7042EVM-PDK_TI(德州仪器)中文资料_英文资料_价格_PDF手册

- TMDS570LS31HDK_TI(德州仪器)中文资料_英文资料_价格_PDF手册

- VCA8500BOARD_TI(德州仪器)中文资料_英文资料_价格_PDF手册

- DEM-SOT223LDO_TI(德州仪器)中文资料_英文资料_价格_PDF手册