ADS7042EVM-PDK、ADS7049-Q1EVM-PDK 和 ADS7057EVM-PDK

评估模块EVAL BOARD FOR ADS7057

本用户指南介绍了 ADS7042EVM-PDK、ADS7049-Q1EVM-PDK 和 ADS7057EVM-PDK 评估模块 (EVM)(统称 为 ADS704X-5XEVM-PDK)的特性、操作和使用。每个套件都用作两个不同的低功耗、小尺寸、通用逐次逼近寄 存器 (SAR) 型模数转换器 (ADC) 的评估平台。这些 ADC 包括 12 位、1MSPS、单端输入 ADS7042;12 位、 2MSPS、单端 ADS7049-Q1;12 位、3MSPS、差分输入 ADS7047 和 14 位、2.5MSPS、差分输入 ADS7057。 此外,独特的 EVM 设计可以通过微小的修改来评估整个 ADS704x 和 ADS705x 器件系列。最后,借助硬件、软 件以及通过通用串行总线 (USB) 接口连接计算机,此 EVM 平台可以简化器件分析。

本用户指南包括完整的电路说明、原理图和物料清单。除非另有说明,否则本文档中的所有缩写词 EVM 以及术语 评估模块 与任何 EVM(ADS7042EVM-PDK、ADS7049-Q1EVM-PDK 或 ADS7057EVM-PDK)具有相同的含 义

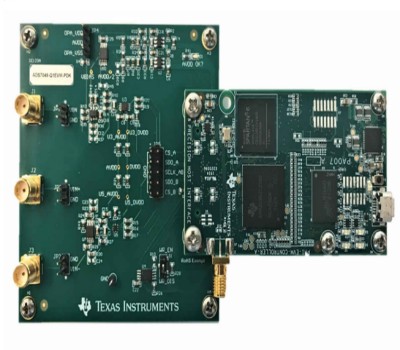

1 ADS704X-5XEVM-PDK 概览

ADS704X-5XEVM-PDK 是一个用于评估 ADS704x 和 ADS705x 系列 ADC 性能的平台。ADS704X-5XEVM-PDK 具有以下特性:

• ADS704X-5XEVM,用于对电路板上的每个 ADC 进行诊断测试和准确的性能评估

• USB 供电 - 无需外部电源

• 精密主机接口 (PHI) 控制器,提供可通过 USB 2.0(或更高版本)方便地连接至每个 ADC 的通信接口,以实 现电力传输以及数字输入和输出

• Microsoft® Windows® 8 和 Windows® 10 操作系统

• 适用于 64 位 Microsoft® Windows® 的易用评估软件

• 一个软件套件,其中包括用于数据捕获、直方图分析和频谱分析的图形用户界面 (GUI) 和工具。该套件还具有 将数据导出至文本文件以便进行后处理的配置

PHI 板主要提供三个功能:

• 通过 USB 端口提供从 EVM 到计算机的通信接口

• 提供与每个 ADC 通信所需的数字输入和输出信号

• 为 ADS704X-5XEVM 板上的所有有源电路供电

每个 ADS704X-5XEVM 板都包含从 ADC 中获取卓越性能所需的外设模拟电路和元件。此外,每个 ADS704X-5XEVM 都包含两个完整的 ADC 信号链:一个支持单端输入 ADC(参阅节 2.1.1),另一个支持差分 输入 ADC(参阅节 2.1.2)。表 1-1 定义了每个 EVM 上默认填充的 ADC。

此外,ADS704X-5XEVM 具有以下特性:

• 来自超小型 A 版 (SMA) 连接器或接头引脚的外部信号源

• 使用外部电源的选项

• 串行接口插头可轻松连接至 PHI 控制器

• 使用逻辑分析仪监控数字信号的引脚连接

• 两个超低噪声、低压降 (LDO) 稳压器,可对所有模拟电路进行出色的单电源稳压

• 适应使用四种不同器件尺寸的 14 种不同 ADC(参照表 1-2)的所有封装选项

2 ADS704X-5XEVM 简介

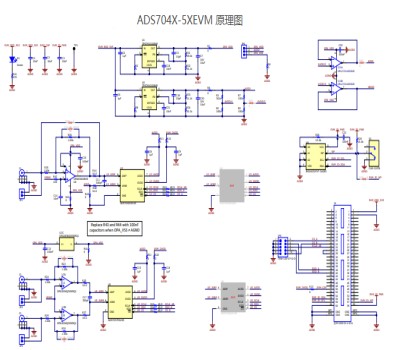

每个 ADS704X-5XEVM 板都包含从每个 ADC 信号链中获得卓越性能所需的外设模拟电路和元件。图 2-1 中突出 显示了 EVM 的重要部分,并在后续部分对此进行介绍。

2.1 模拟输入

如图 2-1 所示,ADS704X-5XEVM 有两条模拟输入路径:一条以红色突出显示的单端输入路径和一条以绿色突出 显示的差分输入路径。每条路径都包含 SMA 连接器和接头,用于连接外部信号。这些信号馈入驱动放大器,然后 馈入两个 ADC 封装之一,其中数字输出通过 J4 提供给 PHI。

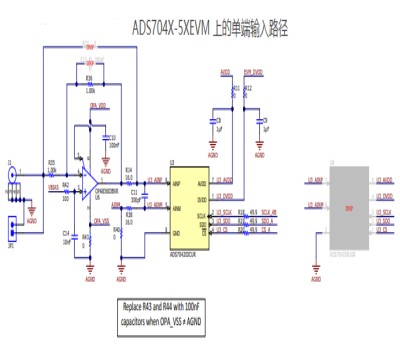

2.1.1 单端输入路径

单端输入路径由一个反相驱动放大器、一个 RC 电路和两个 ADC 封装组成。图 2-2 显示了单端输入路径原理图。

连接到单端输入路径的信号被施加到反相放大器,其共模电压由 VBIAS 设置。放大器的输出连接到 RC 滤波器 (R14、R38 和 C11),然后再连接到 ADC 输入。可以通过 C12 将补偿电容器添加到放大器反馈环路,但不是 实现良好性能所必需的。放大器电源默认连接到 OPA_VDD 和 OPA_VSS 电源。节 2.2 介绍了如何修改 EVM 以 使用外部电源。如果需要,可以通过在 R37 上填充一个 0Ω 电阻并移除 R14 和 R35 来绕过放大器。

还显示了与 ADC (U3) 的所有连接。每个电源连接都有一个 1μF 的去耦电容。电源连接还具有一个 0Ω 的 串联电阻,可移除该电阻以进行外部电流测量。此外,每个数字输入都有一个 49.9Ω 的串联电阻。这些电阻会让 数字信号的边缘变得平滑,以更大限度减少过冲和振铃。

最后,图 2-2 标识了 U8 中的一个不填充 (DNP) 元件。该 ADC 尺寸位于电路板底部,可用于评估采用表 1-2 中所 列 X2QFN 封装的任何单端 ADC。但是,在焊接 U8 中的器件之前,请确保完全移除 U3 中的任何器件。节 4.6 介绍了如何在更换 ADC 时使用 ADS704X-5XEVM GUI 更新 EEPROM。

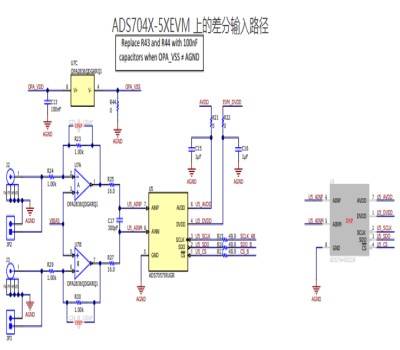

2.1.2 差分输入路径

差分输入路径由一个差分驱动放大器、一个 RC 电路和两个 ADC 封装组成。图 2-3 显示了差分输入路径原理图。

连接到差分输入路径的信号被施加到采用反相配置的差分放大器,其共模电压由 VBIAS 设置。放大器的输出连接 到 RC 滤波器(R25、R27 和 C17),然后再连接到 ADC 输入。每个放大器反馈环路都有一个通过 C23 或 C24 补偿电容器的选项,但这些电容器不是实现良好性能所必需的。放大器电源默认连接到 OPA_VDD 和 OPA_VSS 电源。节 2.2 介绍了如何修改 EVM 以使用外部电源。

还显示了与 ADC (U5) 的所有连接。每个电源连接都有一个 1μF 的去耦电容。电源连接还具有一个 0Ω 的 串联电阻,可移除该电阻,以进行外部电流测量。此外,每个数字输入都有一个 49.9Ω 的串联电阻。这些电阻会 让数字信号的边缘变得平滑,以更大限度减少过冲和振铃。

最后,图 2-3 标识了 U9 中的一个不填充 (DNP) 元件。该 ADC 封装位于电路板底部,可用于评估表 1-2 中采用 VSSOP 封装的任何差分 ADC。但是,在焊接 U9 中的器件之前,请确保完全移除 U5 中的任何器件。节 4.6 介绍 了如何在更换 ADC 时使用 ADS704X-5XEVM GUI 更新 EEPROM。

2.2 电源

EVM 的默认状态是所有电源均来自 USB 电源并由 PHI 控制器提供。3.3V ADC 数字电源电压 (DVDD) 由 PHI 通 过 J4 上的引脚 50 提供(参阅图 2-7)。PHI 还提供一个稳压 5.5V 电源轨,该电源轨馈入 EVM 上的两个 LDO。 这些 LDO 为放大器 (OPA_VDD) 生成低噪声 3.6V(标称)电源电压,为 ADC (AVDD) 生成低噪声 3.3V(标称) 模拟电源电压。图 2-4 显示了 ADS704X-5XEVM 上使用的两个 LDO 电路。

顶部 LDO (U1) 具有由电阻器 R31 和 R32 设置的可调输出,而底部 LDO (U2) 具有由电阻器 R33 和 R34 设置的可调输出。如果需要不同的 OPA_VDD 或 AVDD 电压,请修改这些电阻值。在修改电源时,确保所有 元件的输入、绝对和共模电压限制在数据表限制范围内。有关如何为特定输出电压选择电阻值的更多信息,请参 阅 LDO 数据表。

如果需要外部电源,请移除图图 2-4 中的电阻器 R1 和 R6,以断开两个 LDO 与电源电路的连接。然后可以使用 图 2-5 中的连接器 JP4 为 OPA_VDD、AVDD 和 OPA_VSS 提供直接电源。

如果 OPA_VSS 连接到 AGND 以外的任何电压,请移除图 2-5 中的 R4,并按照图 2-2 中的说明更换 R43 和 R44。如果 OPA_VSS 被修改,另一个重要的考虑因素是,图 2-6 中缓冲放大器上的 V– 输入(引脚 4)硬连线 到 AGND,因此当 OPA_VSS 上的电压改变时,V– 输入不受影响。

缓冲放大器可防止 AVDD/4 电阻分压器(R3 和 R5)加载放大器输入,并防止 AVDD/2 电阻分压器 (R7 和 R9)加载 ADC 输入(参阅图 2-4)。根据节 2.1.1,VBIAS 为两个信号路径设置驱动放大器共模电压。 仅当图 2-2 中的 U3 或 U5 装有 ADS7043 时才需要 AINM。该特定 ADC 具有伪差分输入,需要将 AINM 引脚设 置为 AVDD/2 ± 100mV。

在 ADS704X-5XEVM 上使用 ADS7043 时:

• 使用 0Ω 电阻器填充图 2-4 中的 R39

• 使用 0Ω 电阻器填充图 2-6 中的 R45

• 取消填充图 2-2 中的 R40

2.3 数字接口与通信

EVM 与 PHI 连接,并通过 USB 与计算机进行通信。EVM 上有三个与 PHI 进行通信的器件:两个 ADC(通过 SPI 进行通信)和 EEPROM(通过 I2C 进行通信)。EEPROM 经过预编程,包含配置和初始化 ADS704X-5XEVM 上默认填充的每个 ADC 的信息。因此,仅当用户移除并更换默认 ADC 之一时,才需要与 EEPROM 通信。请参阅节 2.4,了解详情。

ADS704X-5XEVM 支持的所有 ADC 在模式 1(CPOL = 0,CPHA = 1)下使用 SPI 串行通信。由于串行时钟 (SCLK) 频率可高达 60MHz,ADS704X-5XEVM 在 SPI 信号之间提供 49.9Ω 电阻,以确保信号完整性(参阅图 2-2)。通常,在高速 SPI 通信中,快速信号边沿会导致过冲;这些 49.9Ω 电阻会减慢信号边沿速率,以更大限 度减少信号过冲。JP5 提供测试点来测量数字信号,如图 2-7 所示。

2.4 板载 EEPROM 的 I2C 总线

电路与 PHI 板一起使用,以识别 EVM 上填充的特定 ADC 并启用正确的 GUI 设置。在 EVM 操作 期间,用户无需修改此电路或与此电路进行交互。因此,开关 S1 默认设置为启用 EEPROM 写保护,除非根据节 2.1.1 或节 2.1.2 修改 ADC,否则不得更改。根据节 4.6,在使用 ADS704X-5XEVM GUI 更换 ADC 时更新 EEPROM。

- LP8557IEVM_TI(德州仪器)中文资料_英文资料_价格_PDF手册

- LAUNCHXL-F28027F TI(德州仪器)中文资料_英文资料_价格_PDF手册

- DLPDLCR160CPEVM DLP160CP TI(德州仪器)中文资料_英文资料_价格_PDF手册

- THS4631DDAEVM TI(德州仪器)中文资料_英文资料_价格_PDF手册

- DAC3482EVM TI(德州仪器)中文资料_英文资料_价格_PDF手册

- THS4302EVM TI(德州仪器)中文资料_英文资料_价格_PDF手册

- ADS7038Q1EVM-PDK_TI(德州仪器)中文资料_英文资料_价格_PDF手册

- LM3450AEV230V30/NOPB_TI(德州仪器)中文资料_英文资料_价格_PDF手册

- TPS72728DSEEVM-406_TI(德州仪器)中文资料_英文资料_价格_PDF手册

- WL1835MODCOM8A_TI(德州仪器)中文资料_英文资料_价格_PDF手册

- TAS5424BQ1DKDEVM_TI(德州仪器)中文资料_英文资料_价格_PDF手册

- ADS7042EVM-PDK_TI(德州仪器)中文资料_英文资料_价格_PDF手册

- TMDS570LS31HDK_TI(德州仪器)中文资料_英文资料_价格_PDF手册

- VCA8500BOARD_TI(德州仪器)中文资料_英文资料_价格_PDF手册

- DEM-SOT223LDO_TI(德州仪器)中文资料_英文资料_价格_PDF手册