LMH6321MR-EVAL/NOPB

1 General Description

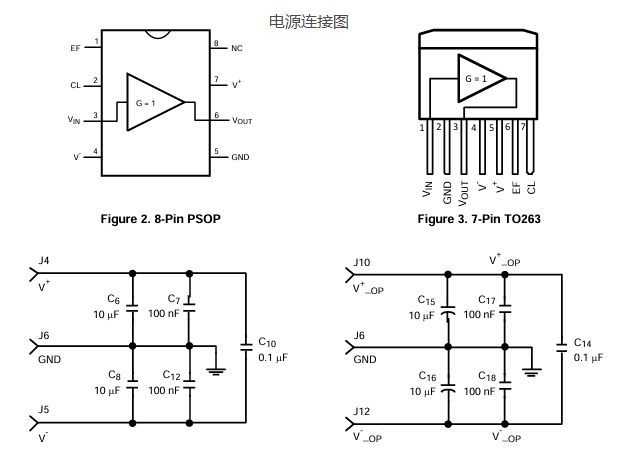

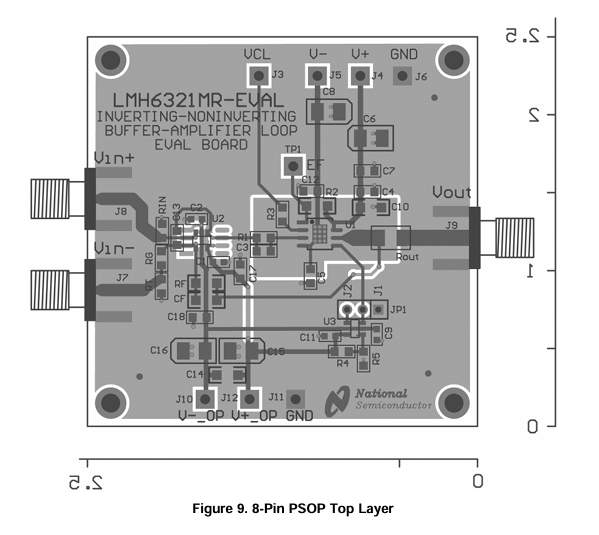

The LMH6321MR-EVAL (for the 8-pin PSOP type package) and the LMH6321TS-EVAL (for the 7-pin TO263 type package) evaluation boards are designed to aid in the characterization of Texas Instruments high speed high current buffers. Use the evaluation boards as a guide for high frequency layout and as a tool to aid in device testing and characterization. Both boards have identical circuit configurations and are designed for either inverting or non-inverting gain.

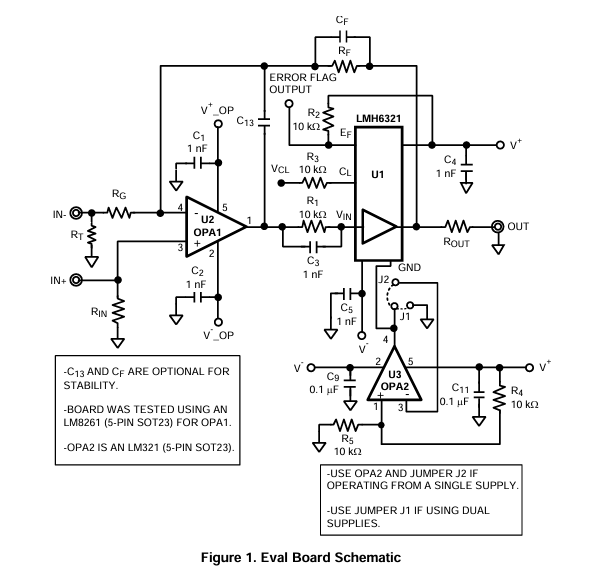

The evaluation board schematic is shown in Figure 1. The schematic shows some of the components with the recommended values. Use all surface-mount components.

2 Connection Diagrams

3 Basic Operation

These boards are a very straight forward design that allows for the evaluation of the LMH6321 in a closed loop configuration with an op amp. Figure 1 shows the schematic for both boards. The input signals are brought into the boards via two SMA connectors to either the inverting or non-inverting inputs. No jumpers or modification of the boards is necessary to use one or the other configurations. The resistors RIN and RT are used to set the input termination resistance to the op amp for non-inverting and inverting operation, respectively. The non-inverting gain is set by Equation 1:NON-INVERTING GAIN: 1 + RF /(RG + RT )The inverting gain is given in Equation 2: INVERTING GAIN: RF /RG

4 The Op Amp

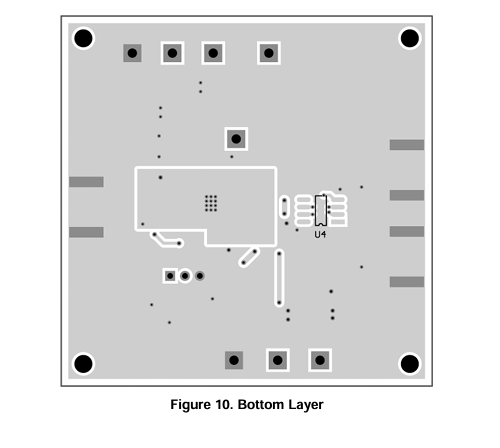

The boards were tested using the LM8261 in a 5-pin SOT23 for OPA1 (pre-assembled boards come equipped with this part), but any single op amp may be used that has the same pin out. In addition, pads for an 8-pin SOIC package are on the opposite side of the board (standard pin out for a single op amp), to increase flexibility in choosing the op amp.

5 Terminating The Board

The output of the buffer travels through a series resistance, and then leaves the board through an SMA connector. ROUT , matches transmission lines or isolates the output from capacitive loads. The SMA board output traces are optimized for connection to a coaxial cable of 50 Ω impedance. That is, the board output traces have a characteristic impedance of 50 Ω, therefore, R4 can also be used to back-match the output cable. However, by changing R4 , other output impedances can be matched, but keep in mind that by using other termination impedances, for example, 75 Ω, the results will be noticeably different, especially for high frequency response. Even with optimal layout, board parasitics play a large part in high frequency performance, and different termination resistors will change the frequency of the dominant parasitic poles and zeros. To suppress transmission line reflections, it is absolutely necessary to have the impedance at the load end of the connected cable matched to the cable impedance. Also, it should be noted that having the output series resistor matched to the cable impedance will give an additional 6 dB of attenuation. If this attenuation is not acceptable, the circuit can be configured in a gain of 2 to compensate.

The value of R4 for terminating a 50 Ω line, or lines, is not 50 Ω. R4 is in series with the effective output impedance of the buffer/driver, RDR , which is typically 5 Ω. Therefore, the value of R4 necessary to match the characteristic line impedance, ZO , should be: R4 = ZO– (N)(RDR ) Where N is the number of driven transmission lines.

5.1 Whenis Termination Needed? Sometimes you can get away with treating a signal line as a simple trace. However, a trace becomes a transmission line at: LENGTH ≥ tr /6 x tpr where, tr is the rise time of a signal pulse and, (3) (4) (5) tpr is the signal propagation rate Typical tpr is about 150 ps/inch on a board of FR-4 material. This formula tells us that the line length beyond which a trace must be treated as a transmission line is a function of rise time and the propagation rate of the signal across the board (a function of board material). When in doubt, always treat the line as a transmission line

6 Output Current Selection

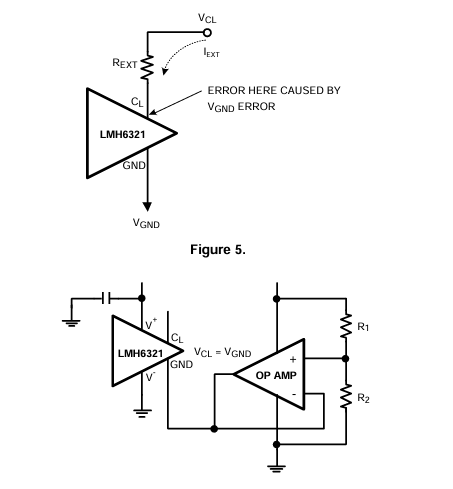

The maximum output current (ISC ) is continuously adjustable between 10 mA and 300 mA, by programming a current (IEXT ) into the CL pin from 25 μA to 750 µA. This is done by connecting a resistor between the CL pin and a DC source (VCL ). This current is given by: IEXT = VCL /REXT for the GND pin equal to zero volts. In the more general case, where VGND is different from zero volts (a single supply is used), then Equation 5 becomes: IEXT = (VCL- VGND )/REXT The relationship between IEXT and ISC is: ISC = 400 IEXT Combining equations Equation 4 and Equation 7, you can write output current in terms of the external resistor, REXT , and programming voltage, VCL . REXT = 400 VCL /ISC (7) (8) (9) (10) (If the VCL pin is left open, the output short circuit current defaults to about 700 mA. At elevated temperatures this current will decrease). As an example, an IEXT of 25 µA or 750 µA will give an ISC of 10 mA or 300 mA, respectively.

As indicated in Figure 1, a 10 kΩ resistor (R3 ) is recommended (though a wide range of resistance values are possible). In this case, the output current can be adjusted directly with VCL over a range of +0.25 V ≤ VCL ≤ +7.5 V , corresponding to 10 mA and 300 mA, respectively.

7 Cautionary Notes

1. As mentioned, if dual supplies are used, then the GND pin can be connected to a hard ground via a jumper wire (this is the way assembled boards are shipped). Although the LMH6321 will most often be used with dual supplies, it can be used with a single supply. In this case the GND pin must be set to a voltage of one VBE (~0.7 V) or greater, or more commonly, mid rail, by a stiff, low impedance source. This precludes the use of a resistive voltage divider. The reason for this is because, when the error flag turns on, a ground current flows out of the GND pin and if a resistive voltage divider were used, this current would produce a voltage drop that would lift the GND pin, thus causing error in the output current. This is because the GND pin is one of the inputs to the error amplifier in the Current Limit circuit, and CL is the other input. This amplifier has a large open loop gain, which forces CL and GND to be at the same potential. Therefore, any error in the GND pin voltage will force the same voltage at the CL pin, which will cause an error in the calculated current limit value. An op amp, configured as a buffered voltage source, can be used to drive the GND pin to 1/2 of V+ when R1 = R2 . The high open loop gain of the op amp forces a very low impedance at the GND pin, which ensures that this pin will be held stiffly at the voltage chosen. The boards come equipped with a circuit that does this. The pin out is standard for an 8 pin single op amp. An LM321 is used on pre-assembled boards, as shown in Figure1

2. A few degrees before the thermal shutdown temperature ( ~160 to 165°C) is reached the part is starting to shutdown and the error flag will show an oscillation. This does not affect the proper functioning of the thermal shutdown. Typical oscillation frequency is 700 to 900 kHz.

3. Keep parasitic capacitance to a minimum at the CL and GND pins, as they are the input and output of an on-chip amplifier configured as a buffer.

4. Adding a buffer inside any op amp feedback loop will add another pole (phase lag) to the response. If the unity gain crossing of op amp is near the gain-bandwidth of the buffer the over-all phase lag of the circuit will consume most, if not all of the available phase margin, and oscillation will occur. For this reason it is important that the buffer has a GBW significantly larger than that of the op amp, so that loop performance will be determined solely by the op amp. With most general purpose, precision, and low power op amps, the bandwidth of the LMH6321 is so great that the op amp totally controls the loop stability. If however, a wideband op amp is used, the phase margin and open loop frequency response can be altered by the additional pole(s) contributed by the buffer and this should be taken into consideration. The buffer phase shift is algebraically summed with the op amp phase shift, and may cause a stable op amp loop to become marginally stable (large overshoot, ringing), depending on the relative positions of the op amp and buffer poles. In the application shown in Figure 1, the LM8261 op amp (OPA1) has a GBW of 15 MHz, while the −3d B bandwidth of the LMH6321 is greater than 100 MHz, giving sufficient loop phase margin. Optional pads have been added to the EVAL boards to allow for the addition of compensating capacitors CC and CF , should they prove necessary.

8 Layout Considerations

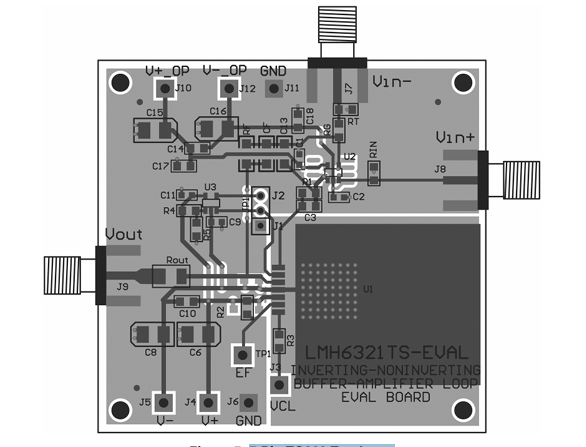

The printed circuit board (PCB) layout and supply bypassing play major roles in determining high frequency performance. When designing you own board use these evaluation boards as a guide and follow these steps to optimize high frequency performance: 1. Use a ground plane 2. Include large (10 μF tantalum) bypass capacitors (C6 and C8 in Figure 1) from both supplies to ground. 3. Use 0.1 nF ceramic capacitors (C1 , C2 , C4 , C5 ) from both supplies to ground as near to the device as practicable. Try to position these less than 0.1 inch from power pins. 4. Remove the ground and power planes from under the input and output pins. 5. Minimize all trace lengths to reduce series inductance 6. Use terminated transmission lines for long signal traces. The op amp and the buffer are powered from different supply pins, allowing for a low voltage op amp to be used even when the buffer is being powered with the full ±15 V it is capable of. The capacitor between both supplies (C10 ) is recommended for best second harmonic distortion performance. The optional zener diode (ZD) between both supplies protects the device from reverse polarity supply connections, under the condition these supplies have the current limit on.

9 Error Flag Operation

The LMH6321 provides an open collector output at the EF pin that produces a low voltage (Flag transistor ON) when the thermal shutdown protection is engaged, due to a fault condition. Under normal operation, the Error Flag pin is pulled to V+ by an external resistor. When a fault occurs that causes the die temperature to rise to about 165°C, the EF pin goes low, but then returns to V+ when the fault disappears. This voltage change can be used as a diagnostic signal to alert a microprocessor of a system fault condition. If this function is used, a 10 kΩ pull-up resistor (R2 in Figure 1) is recommended, but larger resistors can be used. The larger the resistor the lower will be the voltage at this pin under thermal shutdown. Table 1 shows some typical values of VEF for 10 kΩ and 100 kΩ. If the error flag function is not used, the EF pin should be tied to ground

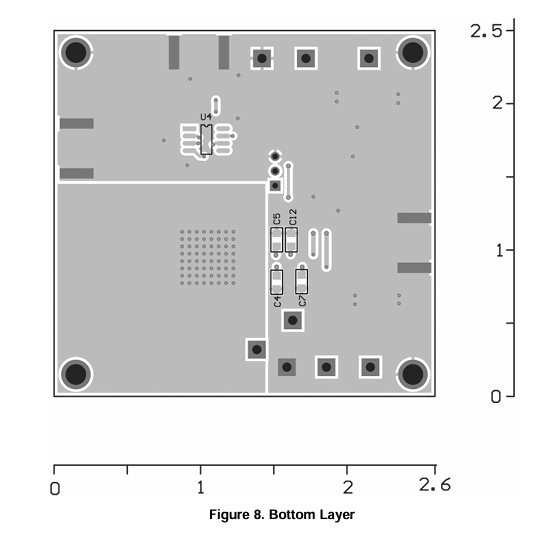

10 BoardLayout

- LP8557IEVM_TI(德州仪器)中文资料_英文资料_价格_PDF手册

- LAUNCHXL-F28027F TI(德州仪器)中文资料_英文资料_价格_PDF手册

- DLPDLCR160CPEVM DLP160CP TI(德州仪器)中文资料_英文资料_价格_PDF手册

- THS4631DDAEVM TI(德州仪器)中文资料_英文资料_价格_PDF手册

- DAC3482EVM TI(德州仪器)中文资料_英文资料_价格_PDF手册

- THS4302EVM TI(德州仪器)中文资料_英文资料_价格_PDF手册

- ADS7038Q1EVM-PDK_TI(德州仪器)中文资料_英文资料_价格_PDF手册

- LM3450AEV230V30/NOPB_TI(德州仪器)中文资料_英文资料_价格_PDF手册

- TPS72728DSEEVM-406_TI(德州仪器)中文资料_英文资料_价格_PDF手册

- WL1835MODCOM8A_TI(德州仪器)中文资料_英文资料_价格_PDF手册

- TAS5424BQ1DKDEVM_TI(德州仪器)中文资料_英文资料_价格_PDF手册

- ADS7042EVM-PDK_TI(德州仪器)中文资料_英文资料_价格_PDF手册

- TMDS570LS31HDK_TI(德州仪器)中文资料_英文资料_价格_PDF手册

- VCA8500BOARD_TI(德州仪器)中文资料_英文资料_价格_PDF手册

- DEM-SOT223LDO_TI(德州仪器)中文资料_英文资料_价格_PDF手册