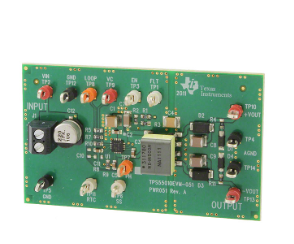

TPS55010EVM-051,Low-Power, Isolated,Fly-buck™ Dual-OutputConverter

Thisuser'sguidecontainsinformationfor theTPS55010EVM-051evaluationmodule(PWR051). Included aretheperformancespecifications, theschematic,andthebillofmaterialsfortheTPS55010EVM-051.

1 Introduction

This user's guide contains background information for the TPS55010 as well as support documentation for the TPS55010EVM-051 evaluation module (PWR051). Included are the performance specifications, the schematic, and the bill of materials for the TPS55010EVM-051.

1.1 Background

The TPS55010EVM-051 is designed to provide dual 40-mA outputs from an input voltage source of 4.5 V to 5.5 V. Rated input voltage and output current range for the evaluation module are given in Table 1 . This evaluation module is designed to demonstrate the small, printed-circuit-board areas that may be achieved when designing with the TPS55010 regulator. The switching frequency is externally set at a nominal 400 kHz. Both high-side and low-side MOSFETs are incorporated inside the TPS55010 package along with the gate drive circuitry. The low drain-to-source on-resistance of the MOSFETs allows the TPS55010 to achieve good efficiency. The compensation components are external to the integrated circuit (IC), and an external divider allows for an adjustable output voltage. Additionally, the TPS55010 provides adjustable slow-start and undervoltage lockout inputs. The absolute maximum input voltage for the TPS55010EVM-051 is 7 V.

1.2 Performance Specification Summary

A summary of the TPS55010EVM-051 performance specifications is provided in Table 2. Specifications are given for an input voltage of VIN = 5 V and an output voltage of 5 V, unless otherwise specified. The TPS55010EVM-051 is designed and tested for VIN = 4 V to 6 V. The ambient temperature is 25°C for all measurements, unless otherwise noted

1.3 Modifications

These evaluation modules are designed to provide access to the features of the TPS55010. Some modifications can be made to this module.

1.3.1 Zener Diode and Output Snubber

Under no-load conditions, VOUT can get as high as ± 30 V if output voltage limiting is not provided. TPS55010EVM-051 provides two Zener diodes (18 V nominal) in series with a resistor to limit the output voltages at J2 to ± 20 V. The Zener diodes present negligible load to the circuit with external loads above approximately 1 mA.

2 Test Setup and Results

This section describes how to properly connect, set up, and use the TPS55010EVM-051 evaluation module. The section also includes test results typical for the evaluation module and covers efficiency, output voltage regulation, load transients, loop response, output ripple, input ripple, and start-up.

2.1 Input/Output Connections

The TPS55010EVM-051 is provided with input/output connectors and test points as shown in Table 3. A power supply capable of supplying 0.5 A must be connected to J1 through a pair of 20 AWG wires. Test-point TP2 provides a place to monitor the VIN input voltages with TP5 providing a convenient ground reference. TP10 and TP13 are used to monitor and load the output voltages with TP4 and TP14 as the ground references.

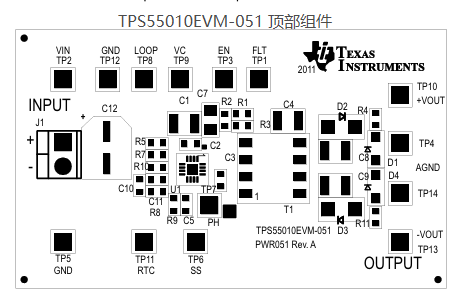

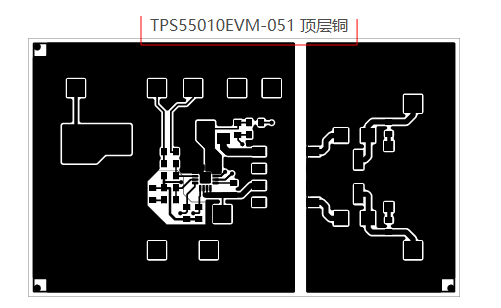

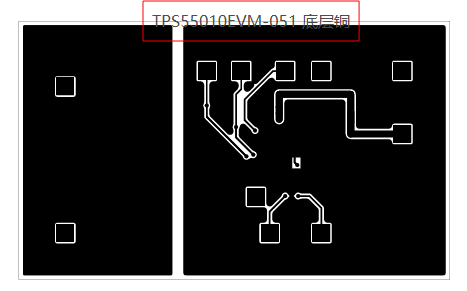

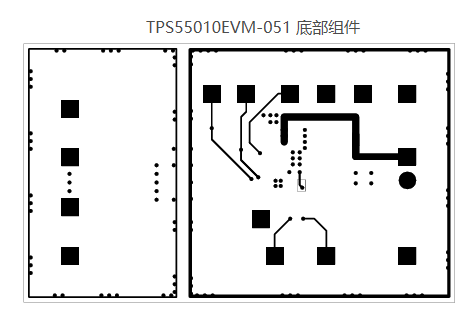

3 Board Layout

This section provides a description of the TPS55010EVM-051, board layout, and layer illustrations.

3.1 Layout

The board layout for the TPS55010EVM-051 is shown in Figure 8 through Figure 11. The top-side layer of the EVM is laid out in a manner typical of a user application. The top and bottom layers are 2-oz copper. A basic set of layout guidelines include:

• Place the input capacitors close to the TPS55010 VIN and GND terminals.

• Arrange the transformer, input capacitors, and the regulated voltage capacitor in a manner to minimize loop area.

• Connect the GND end of the analog control circuitry (COMP, VSENSE, RT/CLK, and SS pins) together apart from the main power GND. Reference this analog GND trace/shape to the power GND ( PowerPAD™ IC package of TPS55010) at a single point.

• ThePowerPAD™ package of the TPS55010 provides a means to remove heat from the device and must be connected to the GND plane with multiple vias as shown in the TPS55010 data sheet, SLVSAV0.

3.2 Estimated Circuit Area

The estimated printed-circuit board area for the components used in this design is 0.70 in2. This area does not include test points or connectors.

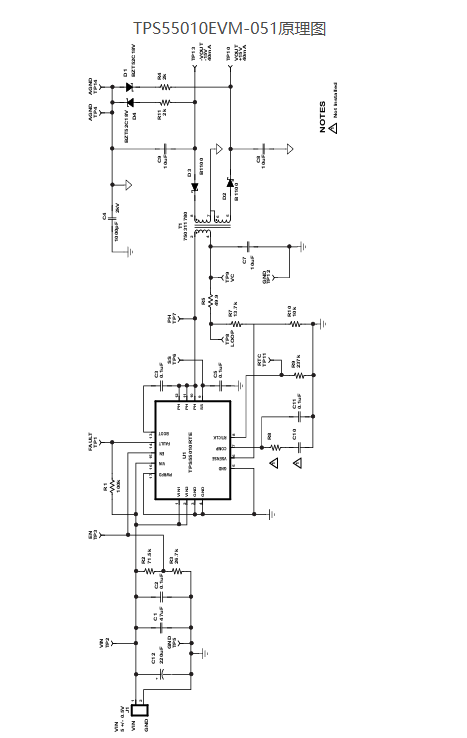

4 SchematicandBillofMaterials

ThissectionpresentstheTPS55010EVM-051schematicandbillofmaterials.

4.1 Schematic

Figure12istheschematicfortheTPS55010EVM-051.

- LP8557IEVM_TI(德州仪器)中文资料_英文资料_价格_PDF手册

- LAUNCHXL-F28027F TI(德州仪器)中文资料_英文资料_价格_PDF手册

- DLPDLCR160CPEVM DLP160CP TI(德州仪器)中文资料_英文资料_价格_PDF手册

- THS4631DDAEVM TI(德州仪器)中文资料_英文资料_价格_PDF手册

- DAC3482EVM TI(德州仪器)中文资料_英文资料_价格_PDF手册

- THS4302EVM TI(德州仪器)中文资料_英文资料_价格_PDF手册

- ADS7038Q1EVM-PDK_TI(德州仪器)中文资料_英文资料_价格_PDF手册

- LM3450AEV230V30/NOPB_TI(德州仪器)中文资料_英文资料_价格_PDF手册

- TPS72728DSEEVM-406_TI(德州仪器)中文资料_英文资料_价格_PDF手册

- WL1835MODCOM8A_TI(德州仪器)中文资料_英文资料_价格_PDF手册

- TAS5424BQ1DKDEVM_TI(德州仪器)中文资料_英文资料_价格_PDF手册

- ADS7042EVM-PDK_TI(德州仪器)中文资料_英文资料_价格_PDF手册

- TMDS570LS31HDK_TI(德州仪器)中文资料_英文资料_价格_PDF手册

- VCA8500BOARD_TI(德州仪器)中文资料_英文资料_价格_PDF手册

- DEM-SOT223LDO_TI(德州仪器)中文资料_英文资料_价格_PDF手册