TLV71312PEVM-171

This user’s guide describes the operational use of the TLV713xxPEVM-171 Evaluation Module (EVM) as a reference design for engineering demonstration and evaluation of the TLV713xxP, low-dropout linear regulator (LDO). Included in this user’s guide are setup instructions, a schematic diagram, layout, thermal guidelines, a bill of materials, and test results.

1 Introduction

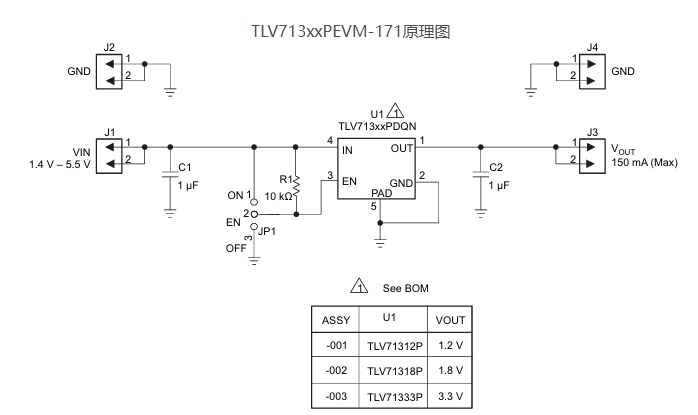

TI's TLV713xxPEVM-171 helps design engineers evaluate the operation and performance of the TLV713xxP family of linear regulators for possible use in their own circuit application. This particular EVM configuration contains a single linear regulator with low Iq, high power supply rejection ratio (PSRR) in a small 1-mm × 1-mm DQN package. The regulator is capable of delivering up to 150 mA to the load depending on the input-output power dissipation across the part which can be minimized because of the low dropout voltage. The output capacitor for the TLV713xxP must be 1 µF (effective minimum) for stability.

2 Setup

This section describes the jumpers and connectors on the EVM as well as how to properly connect, setup, and use the EVM.

2.1 Input/Output Connectors and Jumper Descriptions

2.1.1 J1– VIN

Input power supply voltage connector. Twist the positive input lead and ground return lead from the input power supply and keep them as short as possible to minimize EMI transmission. Add additional bulk capacitance between J1 and J2 if the supply leads are greater than six inches. For example, an additional 47-µF electrolytic capacitor connecting J1 to ground improves the transient response of the TLV713xxP while eliminating unwanted ringing on the input due to long wire connections.

2.1.2 J2– GND

Return connector for the input power supply.

2.1.3 J3– OUT

Regulated output voltage connector.

2.1.4 J4– GND

Output ground return connector.

2.2.5 JP1– EN

Output enable. To enable the output, connect a jumper to short the VIN pin 1 to the EN center pin 2. To disable the output, connect a jumper to short EN pin 2 to GND pin 3. EN is pulled up to VIN through resistor R1 when JP1 is not connected.

2.2 Soldering Guidelines

Any solder re-work to modify the EVM for the purpose of repair or other application reasons must be performed using a hot-air system to avoid damaging the integrated circuit (IC).

2.3 Equipment Interconnect

• Set the input power supply to 5.5 V(max). Turn the power supply off. Connect the positive voltage lead from input power supply to VIN , at the J1 connector of the EVM. Connect the ground lead from the input power supply to GND at the J2 connector of the EVM.

• Connect a 0–150-mA load between the output, OUT, at connector J3, and ground, GND, at connector J4.

• Disable the output by jumping JP1, the EN pin to the OFF pin.

3 Operation

This section provides typical performance waveforms for the EVM. Actual performance data can be affected by measurement techniques and environmental variables; therefore, these curves are presented for reference and may differ from actual results obtained by some users.

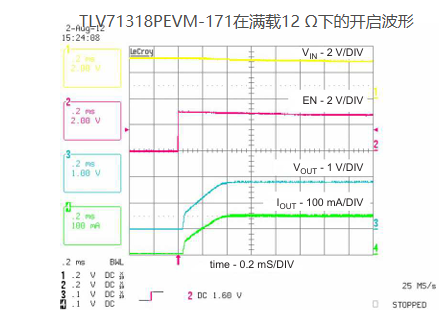

4.1 Turn-on Waveform

Figure 1 shows the turn-on characteristic where 3 V is applied to VIN . The output drives a 12-Ω load (full load).

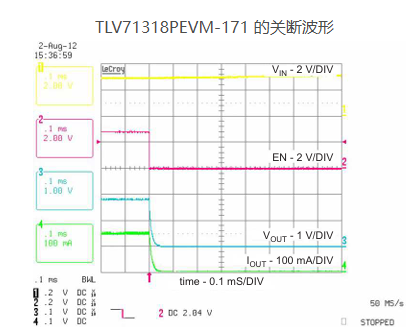

4.2 Turn-off Waveform

Figure 2 shows the turn-off characteristic where 3 V is applied to VIN . The output drives a 12-Ω load.

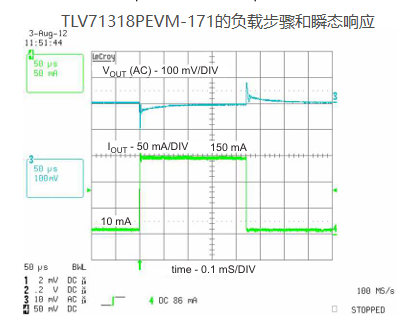

4.3 Load Transient

Figure 3 shows the load transient response for a load step transient from 10 mA to 150 mA where 3 V is applied to VIN .

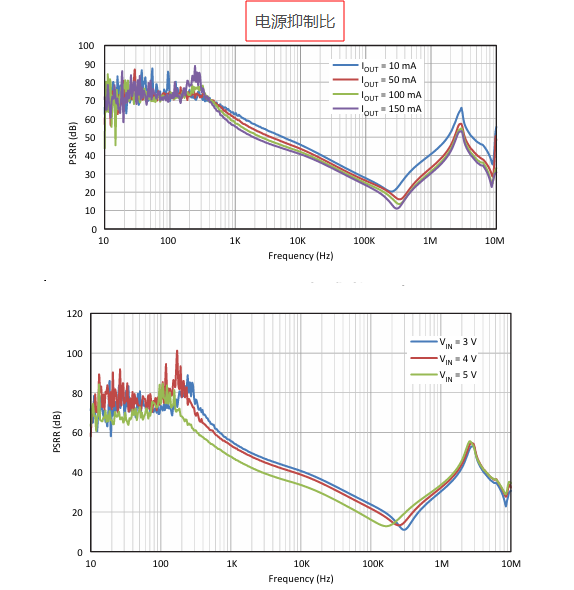

4.4 PSRR

Figure 4 shows the PSRR of the TLV71318EVM-171 at different load currents and Figure 5 shows the PSRR of the TLV71318PEVM-171 at different input voltages.

5 ThermalGuidelinesandLayoutRecommendations

Thermalmanagement isakeycomponentof thedesignofanypowerconverterandisespecially importantwhenthepowerdissipationintheLDOishigh.Usethefollowingformulatoapproximatethe maximumpowerdissipationfortheparticularambient temperature:TJ =TA +PD ×θJA

WhereTJ isthejunctiontemperature,TA istheambient temperature,PD isthepowerdissipationinthe device(Watts),andθJA isthethermal resistancefromjunctiontoambient.All temperaturesareindegrees Celsius.Themaximumoperatingjunctiontemperature,TJ ,mustnotbeallowedtoexceed125°C.The layoutdesignmustbecoppertraceandplaneareassmartly,asthermalsinks, inordernot toallowTJ to exceedtheabsolutemaximumratingunderall temperatureconditionsandvoltageconditionsacrossthe part.

Table1repeatsinformationfromtheDissipationRatingsTableof theTLV713xxPseriesdatasheet for comparisonwiththethermal resistance,θJA , forHigh-KJEDECstandardboards.Themaximuminput voltagecanbecalculatedforfull loadsatdifferentambient temperatures.Theinputvoltagemustbeless thanthesevaluesinordertomaintainasafejunctiontemperature.

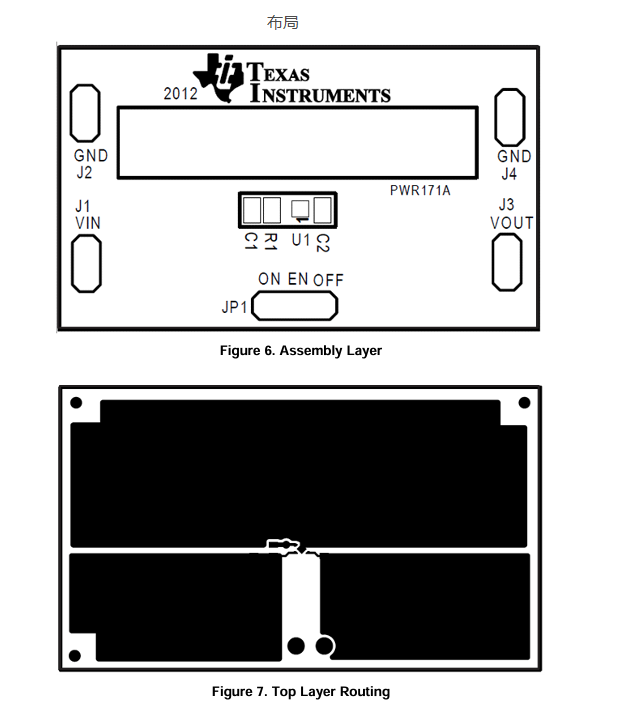

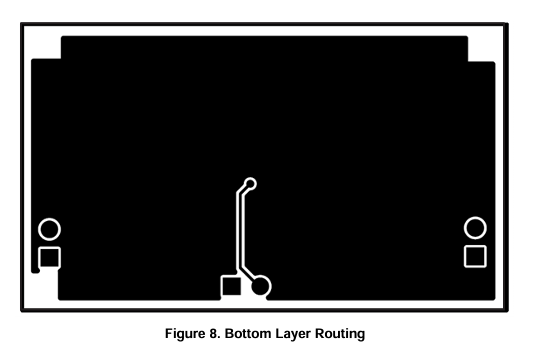

6 Board layout

7 Schematic

- LP8557IEVM_TI(德州仪器)中文资料_英文资料_价格_PDF手册

- LAUNCHXL-F28027F TI(德州仪器)中文资料_英文资料_价格_PDF手册

- DLPDLCR160CPEVM DLP160CP TI(德州仪器)中文资料_英文资料_价格_PDF手册

- THS4631DDAEVM TI(德州仪器)中文资料_英文资料_价格_PDF手册

- DAC3482EVM TI(德州仪器)中文资料_英文资料_价格_PDF手册

- THS4302EVM TI(德州仪器)中文资料_英文资料_价格_PDF手册

- ADS7038Q1EVM-PDK_TI(德州仪器)中文资料_英文资料_价格_PDF手册

- LM3450AEV230V30/NOPB_TI(德州仪器)中文资料_英文资料_价格_PDF手册

- TPS72728DSEEVM-406_TI(德州仪器)中文资料_英文资料_价格_PDF手册

- WL1835MODCOM8A_TI(德州仪器)中文资料_英文资料_价格_PDF手册

- TAS5424BQ1DKDEVM_TI(德州仪器)中文资料_英文资料_价格_PDF手册

- ADS7042EVM-PDK_TI(德州仪器)中文资料_英文资料_价格_PDF手册

- TMDS570LS31HDK_TI(德州仪器)中文资料_英文资料_价格_PDF手册

- VCA8500BOARD_TI(德州仪器)中文资料_英文资料_价格_PDF手册

- DEM-SOT223LDO_TI(德州仪器)中文资料_英文资料_价格_PDF手册