DAC8560EVM-PDK

KIT PERFORMANCE DEMO FOR DAC8560

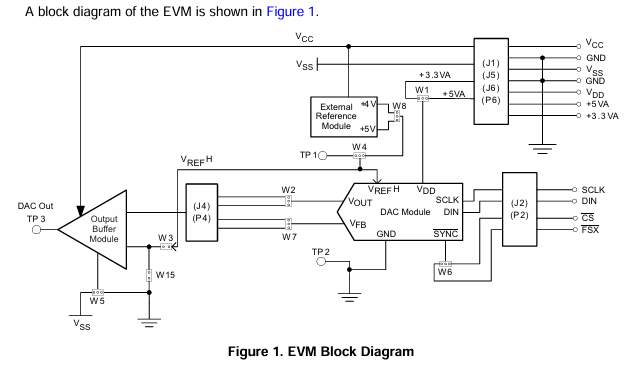

Thisuser’sguidedescribesthecharacteristics,operation,andtheuseof theDAC8560evaluationmodule (EVM). ItcoversallpertinentareastoproperlyusethisEVMboardalongwiththedevicesthat itsupports. ThephysicalPCBlayout,schematicdiagram,andcircuitdescriptionsareincluded.

1 EVM Overview

This section gives a general overview of the DAC8560 evaluation module (EVM), and describes some of the factors to consider when using this module.

1.1 Features

This EVM features the DAC8560 digital-to-analog converter (DAC). The DAC8560EVM is a simple evaluation module designed to quickly and easily evaluate the functionality and performance of the 16-bit high-resolution, single-channel, and serial input DAC with a built-in 2.5-V internal reference that is enabled by default. This EVM features a serial interface to communicate with any host microprocessor or TI DSP base system.

Although the DAC was designed for single-supply operation, a bipolar output range is also possible by configuring the output operational amplifier circuit properly. This is discussed in detail in section 3.2.3. In addition, the external operational amplifier is also installed as an option to provide output signal conditioning or boost capacitive load drive and for other output mode requirements desired.

A +5-V precision voltage reference is provided via U3 as well as a 4.096-V precision reference via U4. These references are optional voltage reference provided externally in case the user needs to evaluate the DAC8560 with external reference circuits. The external +5-V and +4-V reference source can be selected via W8 and W4 jumper configuration.

There is also a provision for possibly experimenting with different circuit loads on the reference of the DAC8560. These are available through R16, C6, and a small 4x4 through-hole grid.

1.2 Power Requirements

The following sections describe the power requirements of this EVM.

1.2.1 Supply Voltage

The dc power supply requirement for this DAC8560EVM (VDD) is selectable between +3.3 V and +5 V via the W1 jumper header. The +3.3 V comes from J6-8 and the +5 V comes from J6-3 terminal. These power-supply voltages are referenced to ground through the J6-6 terminal. The VSS and VCC are only used by the U2 operational amplifier and the U3 voltage reference, which ranges from-15 V to +15 V maximum and connects through J6-1 and J6-2 terminals, respectively. All the analog power supplies are referenced to analog ground through J6-6 terminal.

1.2.2 Reference Voltage

The DAC8560 comes with a +2.5-V internal reference that is enabled by default. The +2.5-V internal reference can be measured from its VREF pin, which can be used to source other devices that requires +2.5-V reference. Because the DAC8560’s internal reference is enabled by default, care should be taken to ensure that the W4 and W8 jumper headers are open. Otherwise, inaccurate performance or damage to the part can result. However, the DAC8560 should not be damaged, providing that the external voltage that is applied to the VREF pin does not exceed the applied voltage in the VDD pin, and it does not exceed 100 mA of sourcing current. It is not recommended to leave the external voltage applied on the VREF pin if the internal reference is not disabled. The external reference source should be disconnected immediately, and the EVM power must be recycled to ensure correct performance of the device.

The +5-V and +4-V precision voltage references are provided as an optional reference source to supply the external voltage reference for the DAC through REF02 (U3) and REF3240 (U4). These reference voltages are selectable via the jumper W8. When shorting pins 1 and 2, the +5-V reference is selected whereas shorting pins 2 and 3 selects +4-V reference. The jumper W4 must be shorted between pins 1 and 2 in order for these reference sources to propagate through the DAC.

The +5-V reference voltage goes through an adjustable 100-kΩ potentiometer, R11, in series with 20-kΩ R10, to allow the user to adjust the reference voltage to its desired settings. The voltage reference then is buffered through U5 as seen by the device under test. The REF02 precision reference is powered by VCC (+15 V) through J6-1 terminal.

The REF3240 precision reference is powered by +5 VA through J6-3 terminal.

The test point TP1 also is provided, as well as J4-20, to allow the user to connect other external reference source if the onboard reference circuit is not desired. The external voltage reference should not exceed the applied power supply, VDD , of the DAC under test.

1.3 EVMBasic Functions

This EVM is designed primarily as a functional evaluation platform to test certain functional characteristics of the DAC8560 digital-to-analog converter (DAC). Functional evaluation of the installed DAC device can be accomplished with the use of any microprocessor, TI DSP, or some sort of a signal/waveform generator.

The headers J2 (top side) and P2 (bottom side) are pass-through connectors provided to allow the control signals and data required to interface a host processor or waveform generator to the DAC8560EVM using a custom-built cable.

The DAC output can be monitored through the selected pins of J4 header connector. The output can be switched through its respective jumper W2 whereas the sense pin VFB also can be switched through its respective jumper W7 for the reason of stacking. The VFB pin is discussed further in section 3 of this user’s guide manual. Stacking allows a total of two (DAC8560) DAC channels to be used provided the frame synchronization signal, SYNC, is unique for each EVM board stacked.

In addition, the option of selecting the DAC output to be fed to the noninverting side of the output operational amplifier, U2, is also possible by using a jumper across the selected pins of J4. The output operational amplifier, U2, must be first configured correctly for the desired waveform characteristic (see Section 3 of this document).

2 PCB Design and Performance

This section discusses the layout design of the PCB, describes the physical and mechanical characteristics of the EVM, and provides a brief description of the EVM test performance procedure. Also included is the list of components used on this evaluation module.

2.1 PCBLayout

The DAC8560EVM is designed to preserve the performance quality of the DAC, device under test, as specified in the data sheet. To take full advantage of the EVM's capabilities, use care during the schematic design phase to properly select the right components and to build the circuit correctly. The circuit should include adequate bypassing, identifying and managing the analog and digital signals, and understanding the components' electrical and mechanical attributes.

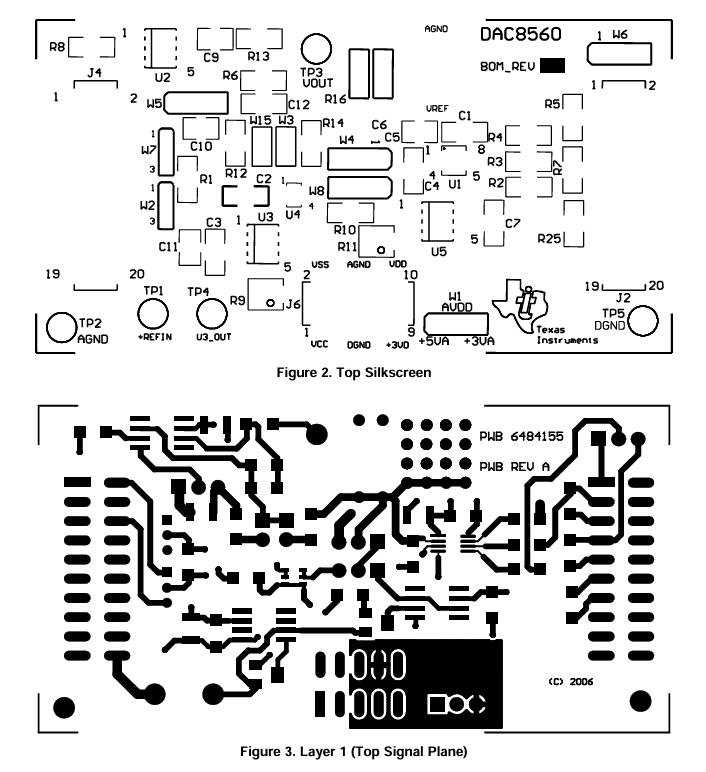

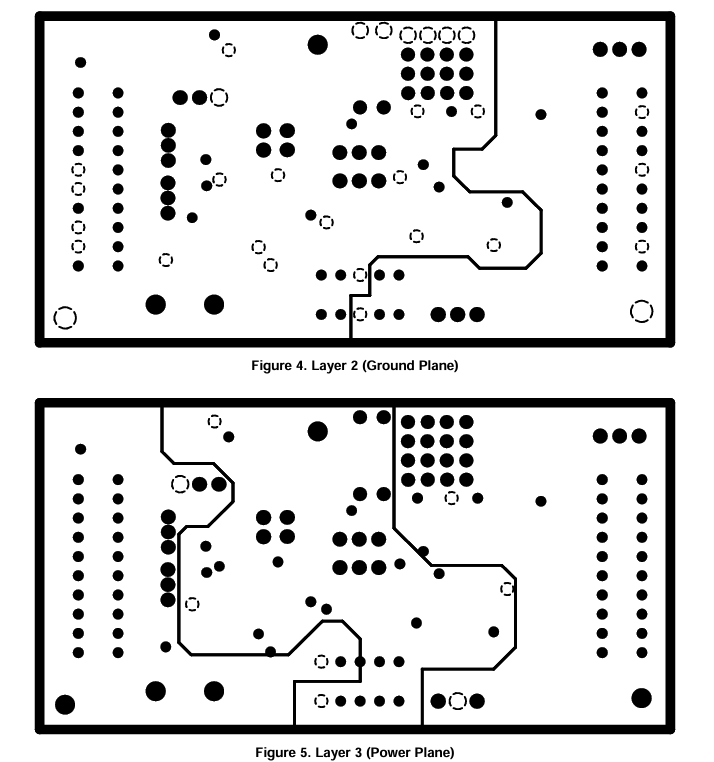

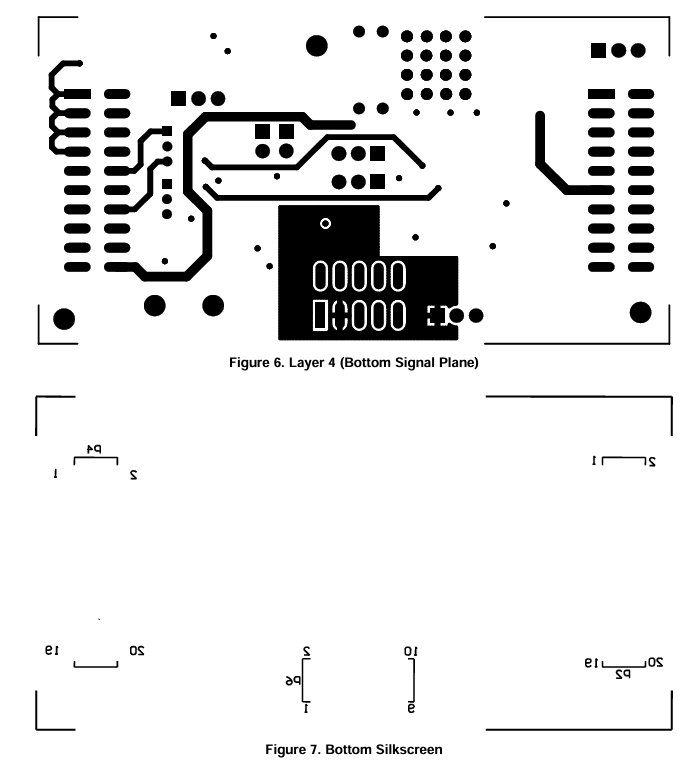

The main design concern during the layout process is the optimal placement of components and the proper routing of signals. Place the bypass capacitors as close as possible to the pins; properly separate the analog and digital signals from each other. In the layout process, carefully consider the power and ground plane because of their importance. A solid plane is ideally preferred, but because of its greater cost, sometimes a split plane can be used satisfactorily. When considering a split plane design, analyze the component placement and carefully split the board into its analog and digital sections starting from the DUT. The ground plane plays an important role in controlling the noise and other effects that otherwise contributes to the error of the DAC output. To ensure that the return currents are handled properly, route the appropriate signals only in their respective sections, meaning that the analog traces should only lay directly above or below the analog section and the digital traces in the digital section. Minimize the length of the traces but use the biggest possible trace width allowable in the design. These design practices are illustrated in Figure 2 through Figure 7.

The DAC8560EVM board is constructed on a four-layer printed-circuit board using a copper-clad FR-4 laminate material. The printed-circuit board has a dimension of 43,1800 mm (1.7000 inch) × 82,5500 mm (3.2500 inch), and the board thickness is 1,5748 mm (0.062 inch). Figure 2 through Figure 6 show the individual artwork layers.

2.2 EVMPerformance

The EVM performance test is performed using a high-density DAC bench test board, an Agilent 3458A digital multimeter, and a PC running the LabVIEW® software. The EVM board is tested for all codes of 65535 and the device under test (DUT) is allowed to settle for 1 ms before the meter is read. This process is repeated for all codes to generate the measurements for INL and DNL.

3 EVM Operation

This section covers in detail the operation of the EVM to provide guidance to the user in evaluating the onboard DAC and how to interface the EVM to a specific host processor.

See the DAC8560 data sheet, SLAS264, for information about its serial interface and other related topics.

The EVM board is factory tested and configured to operate in the unipolar output mode.

3.1 Factory Default Settings

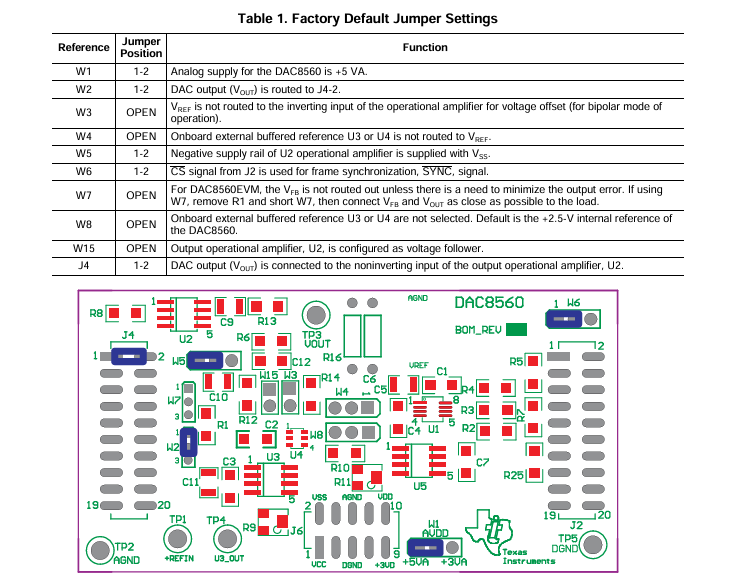

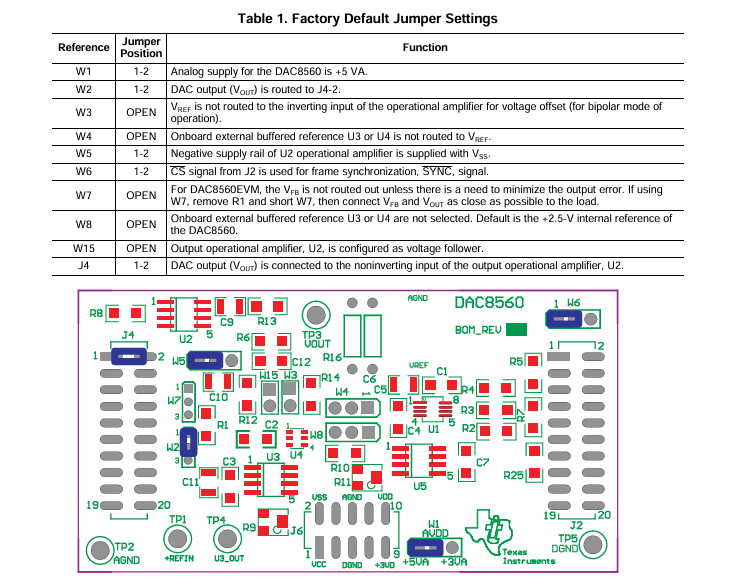

The EVM board is set to its default configuration from factory as described in Table 1 to operate in unipolar +2.5-V mode of operation. Figure 9 shows the default jumper configuration as described in the table for the DAC8560.

- LP8557IEVM_TI(德州仪器)中文资料_英文资料_价格_PDF手册

- LAUNCHXL-F28027F TI(德州仪器)中文资料_英文资料_价格_PDF手册

- DLPDLCR160CPEVM DLP160CP TI(德州仪器)中文资料_英文资料_价格_PDF手册

- THS4631DDAEVM TI(德州仪器)中文资料_英文资料_价格_PDF手册

- DAC3482EVM TI(德州仪器)中文资料_英文资料_价格_PDF手册

- THS4302EVM TI(德州仪器)中文资料_英文资料_价格_PDF手册

- ADS7038Q1EVM-PDK_TI(德州仪器)中文资料_英文资料_价格_PDF手册

- LM3450AEV230V30/NOPB_TI(德州仪器)中文资料_英文资料_价格_PDF手册

- TPS72728DSEEVM-406_TI(德州仪器)中文资料_英文资料_价格_PDF手册

- WL1835MODCOM8A_TI(德州仪器)中文资料_英文资料_价格_PDF手册

- TAS5424BQ1DKDEVM_TI(德州仪器)中文资料_英文资料_价格_PDF手册

- ADS7042EVM-PDK_TI(德州仪器)中文资料_英文资料_价格_PDF手册

- TMDS570LS31HDK_TI(德州仪器)中文资料_英文资料_价格_PDF手册

- VCA8500BOARD_TI(德州仪器)中文资料_英文资料_价格_PDF手册

- DEM-SOT223LDO_TI(德州仪器)中文资料_英文资料_价格_PDF手册