THS3217EVM

EVALUATION MODULE

This user guide describes the characteristics, operation, and use of the THS3215EVM and THS317EVM (THS321xEVM). This evaluation module (EVM) is a demonstration fixture for the THS3215 andTHS3217 family of wideband, differential DAC to single-ended line drivers. The EVM provides 50-Ω input and output termination for easy evaluation with common 50-Ω test equipment. A complete circuit description, schematic diagram, printed circuit board (PCB) layout, and bill of materials are included

Throughout this document, the terms demonstration kit, evaluation board, evaluation module, and EVM are synonymous with the THS321xEVM.

1 Introduction

This section provides a general description of the THS3215 and THS3217 devices and the EVM.

1.1 THS3215 and THS3217 Description

The THS3215 and THS3217 (THS321x) combine the key signal-chain components required to interface with a complementary-current output, digital-to-analog converter (DAC). These two-stage devices deliver the low-distortion, dc-coupled, single-ended signal required by a wide range of applications. The input stage buffers the DAC resistive termination, and converts the signal from differential to single-ended with a fixed gain of 2 V/V. The differential to single-ended output is available externally for direct use, and can also be connected through an RLC filter or attenuator to the input of an internal output power stage (OPS). The wideband, current-feedback, OPS provides all pins externally for flexible gain setting.

An internal 2 × 1 multiplexer (mux) to the OPS noninverting input provides an easy means to select between the internal differential-to-single ended stage (D2S) output or an external input. More information on the THS3215 and THS3217 can be found in their respective product data sheets, SBOS780 and SBOS766.

1.2 EVM Description

The THS321xEVM enables performance evaluation of each individual subblock within these devices. The PCB provides various flexible options to also test either the THS3215 or THS3217 as a complete system. The EVM provides placeholders to insert filters at different points within the system to allow for more realistic end-application evaluation.

The following list describes key EVM components:

• Power input: ±6 VDC (typical) at +VCC (P3, TP1) and –VCC (P1, TP2)

• Common reference: GND (P2, TP3 and TP13)

• Interface to the midscale buffer input pin, VMID_IN, through J3 (TP8).

• Interface to the midscale buffer output pin, VMID_OUT, through J4 (TP9).

• Interface to the D2S noninverting signal input pin, IN+, through J1 (TP4).

• Interface to the D2S inverting signal input pin, IN–, through J2 (TP5).

• Interface to the D2S output pin, VO1, through J5 (TP14)

• Interface to the D2S reference input, VREF, through J4. SMA connector J4 is shared with the midscale buffer output. Depending on the components populated on the board, the appropriate signal is available at the SMA connector.

• PATHSEL control though switch CS_SW (TP12). Section 2.2 describes the operation of the switch logic.

• Interface to the OPS external, noninverting input pin, VIN+, through J8.

• DISABLE control though switch PD_SW (TP11). Section 2.2 describes the operation of the switch logic.

• Interface to the OPS output pin, VOUT, through J7 (TP10).

• Interface to the OPS inverting input pin, VIN–, through J6.

2 Design Considerations

This section discusses general design considerations and options when setting up and configuring the various blocks in THS321xEVM.

2.1 Power Supplies

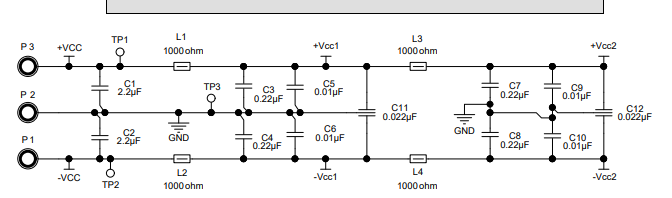

Power is applied to the board through connectors P1, P2, and P3, as shown in Figure 1. Both bipolar and single-sided supplies can be used. The typical supplies are ±6 V.

2.2 Digital Logic Control

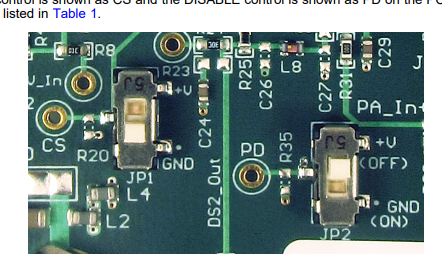

There are two bidirectional switches on the THS321xEVM that control the status of the PATHSEL and DISABLE control pins. Figure 2 shows the control logic with respect to the switch position. For brevity, the PATHSEL control is shown as CS and the DISABLE control is shown as PD on the PCB. The full switch settings are listed in Table 1.

2.3 Midscale or Reference Buffer

The EVM is configured by default to drive a ground-centered signal. In cases where a different output common-mode voltage is required, use the midscale buffer to provide a low impedance path. This buffer is also used in applications where a servo loop is required to set the dc offset of the system to a desired value. Alternatively, the buffer can also be used to set the reference voltage in single-supply applications where the inputs to the D2S are ac-coupled. The midscale buffer input defaults to the midsupply voltage. In cases where a different input voltage is required, adjust the R14 potentiometer (uninstalled by default) to achieve the desired offset voltage. Resistor R62 must be appropriately sized, and resistor R63 uninstalled in order to set the correct voltage at the input of the midscale buffer. The EVM allows for connecting the output of the midscale buffer to various nodes of the THS321x. The different options are:

1. In single-supply and ac-coupled applications, the common-mode input of the D2S is configured in one of two ways. The first way is by installing R56 = 0 Ω. This setting connects the output of the buffer to the Junc_Vocm node on the board. Components R5, R6, R11, and C19 must be appropriately sized and installed. The second way is by applying an external common-mode voltage through test-point TP7.

2. If the output common-mode voltage of the D2S must be set to any voltage other than GND, uninstall resistors R54 and R51, and install R48 instead. This configuration connects the output of the midscale buffer to VREF (pin 14).

3. If the OPS is configured in the noninverting mode with a common-mode dc offset voltage from the D2S, then the D2S provides the necessary dc bias to the noninverting pin of the OPS. However, if the OPS RG is grounded, the dc common-mode offset voltage from the D2S is amplified by (1 + RF / RG), and may result in limited output headroom from the OPS. To prevent this limitation, connect RG to the midscale buffer output so that the common-mode gain is 0 dB by setting R55 to the desired value of the gain resistor and uninstalling R42. Installing R55 connects the output of the midscale buffer to Junc_Vneg enabling configuration of the OPS in a level-shifted, common-mode, noninverting configuration. Make sure that R54 and R60 are uninstalled, and R51 = R53 = 0 Ω in this configuration.

The areas within the dashed boxes in Figure 3 show the described configurations.

2.4 Differential to Single-Ended Stage (D2S)

The D2S inputs are driven by an external differential signal through SMA connectors J1 and J2. Standard lab equipment usually provides only a single-ended output. The LMH3401, a very wideband, single-ended to differential amplifier, was used during product evaluation to drive a differential signal into the D2S. The spacing of the SMA connectors on the THS321xEVM is designed to interface directly with the output of the LMH3401EVM through standard SMA barrel connectors. The THS321xEVM provides a standard 100- Ω differentially-terminated resistive network to GND, dc-coupled to the D2S input pins. Figure 4 shows the EVM schematic of the D2S input/output network with the default passive components installed. The output of the D2S can also be measured externally at J5.

The EVM allows for flexibility in the D2S input network configuration. The different options are: 1. In order to reduce the high-frequency noise and distortion components from the previous stage driving the D2S, a passive RLC filter can be inserted prior to the D2S inputs. Figure 5 shows an example of a third-order, 200-MHz, Butterworth filter placed between the DAC output and D2S input. The THS321xEVM is able to evaluate system performance with similar RLC-filter architectures installed on the board.

- LP8557IEVM_TI(德州仪器)中文资料_英文资料_价格_PDF手册

- LAUNCHXL-F28027F TI(德州仪器)中文资料_英文资料_价格_PDF手册

- DLPDLCR160CPEVM DLP160CP TI(德州仪器)中文资料_英文资料_价格_PDF手册

- THS4631DDAEVM TI(德州仪器)中文资料_英文资料_价格_PDF手册

- DAC3482EVM TI(德州仪器)中文资料_英文资料_价格_PDF手册

- THS4302EVM TI(德州仪器)中文资料_英文资料_价格_PDF手册

- ADS7038Q1EVM-PDK_TI(德州仪器)中文资料_英文资料_价格_PDF手册

- LM3450AEV230V30/NOPB_TI(德州仪器)中文资料_英文资料_价格_PDF手册

- TPS72728DSEEVM-406_TI(德州仪器)中文资料_英文资料_价格_PDF手册

- WL1835MODCOM8A_TI(德州仪器)中文资料_英文资料_价格_PDF手册

- TAS5424BQ1DKDEVM_TI(德州仪器)中文资料_英文资料_价格_PDF手册

- ADS7042EVM-PDK_TI(德州仪器)中文资料_英文资料_价格_PDF手册

- TMDS570LS31HDK_TI(德州仪器)中文资料_英文资料_价格_PDF手册

- VCA8500BOARD_TI(德州仪器)中文资料_英文资料_价格_PDF手册

- DEM-SOT223LDO_TI(德州仪器)中文资料_英文资料_价格_PDF手册